Bild

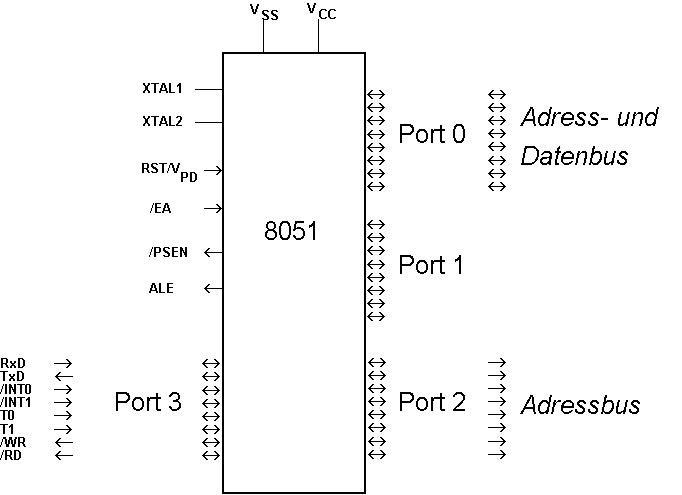

3.1. Logisches Symbol des 8051

Tabelle 3.1. Pin-Definitionen und

Funktionen der 8051 DIL-Version

|

Symbol |

Pin |

Input

I Output

O |

Funktionen |

|

Vss |

20 |

|

O-Potential - Digitale Masse |

|

Vcc |

40 |

|

+5V

Spannungsversorgung |

|

XTAL1 |

19 |

|

Eingang

zum Oszillatorverstärker. Wird gebraucht, wenn ein Quarz benutzt wird. Wird

mit Vss verbunden, wenn eine externe Quelle an XTAL2 benutzt wird. |

|

XTAL2 |

18 |

|

Ausgang

vom Oszillatorverstärker. Eingang zum internen Timing-Teil. Ein Quarz oder

eine externe Quelle kann benutzt werden. |

|

RST/VPD |

9 |

I |

Reset

- Ein 1-Pegel setzt den Baustein zurück. Ein kleiner, interner

Pulldown-Widerstand erlaubt beim Einschalten ein Reset nur durch Zuschalten

eines einfachen Kondensators. Weiterhin kann der VVPD zum Steuern von

standby power verwendet werden. |

|

/EA |

31 |

I |

Bei

0-Pegel holt der 8051 alle Instruktionen vom externen Programmspeicher. Bei

1-Pegel bis zu den Adressen 4096, d.h. die unteren 2KByte vom internen

Speicher. |

|

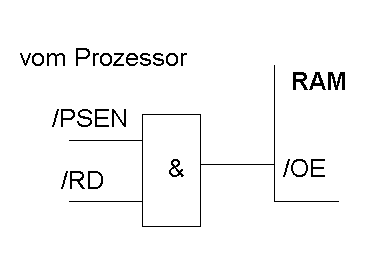

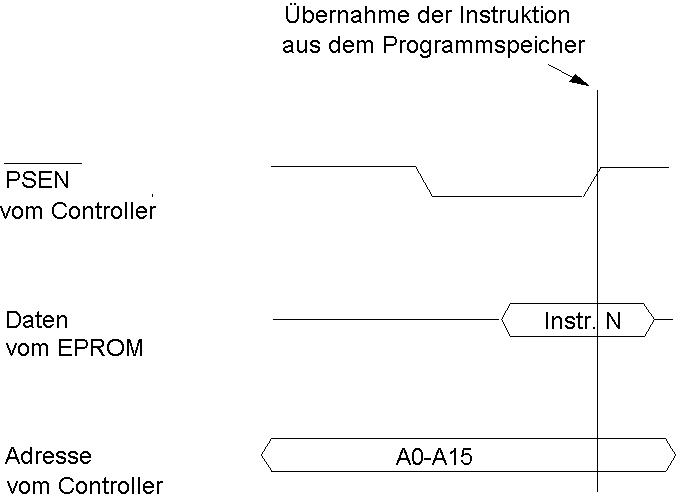

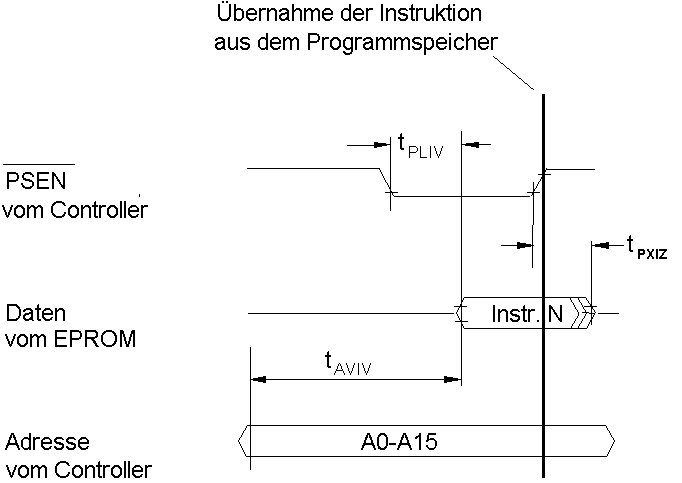

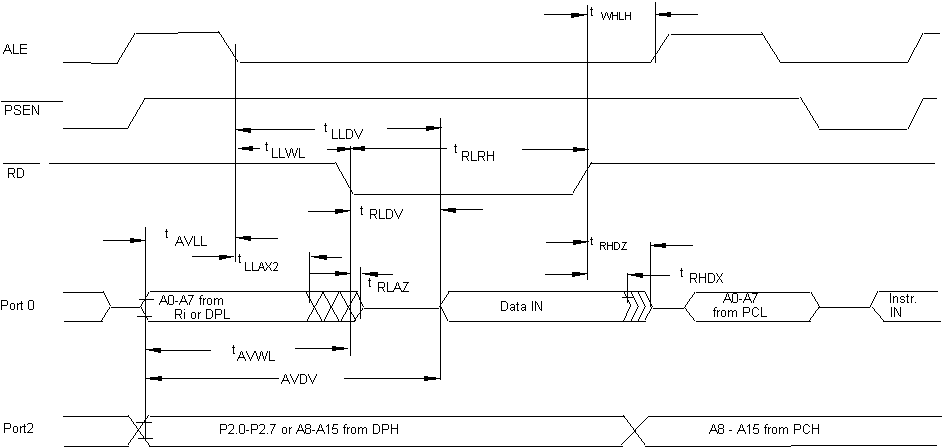

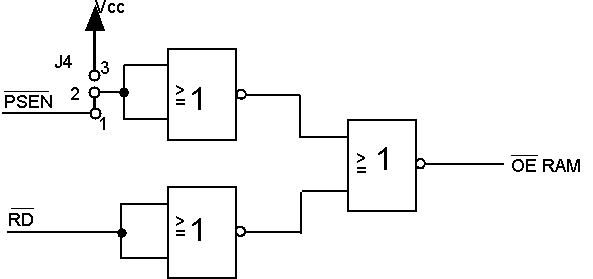

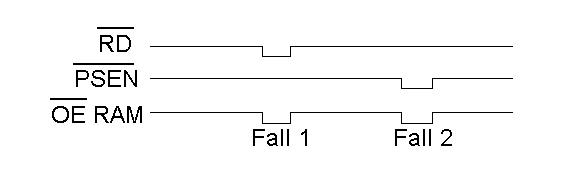

/PSEN |

29 |

O |

Program Storage Enable. Ist ein zum Controlbus

gehöriges Signal für den externen Programmspeicherzugriff. Es wird alle 6

Oszillatorperioden aktiviert. Es bleibt auf 1-Pegel, wenn interner

Programmspeicherzugriff erfolgt. |

|

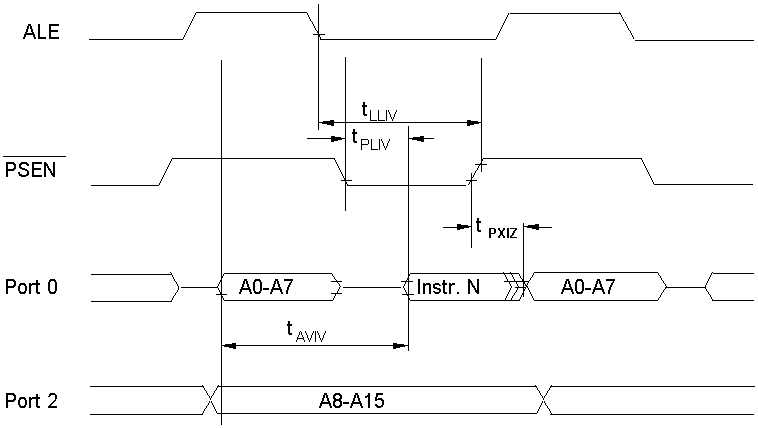

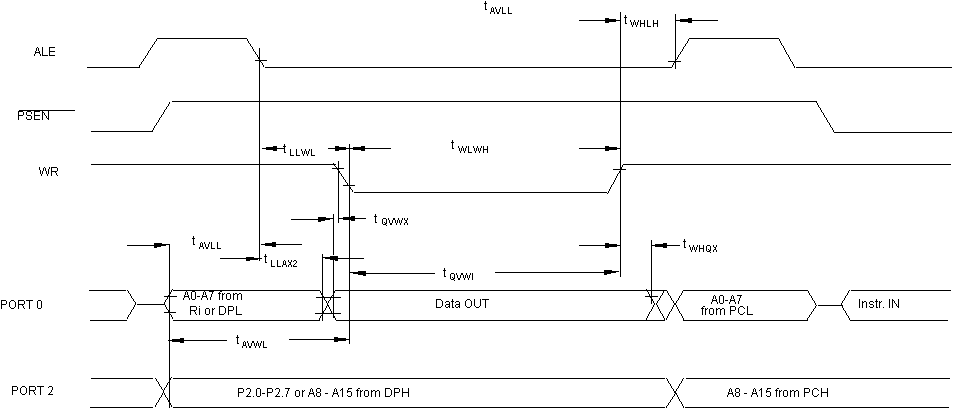

ALE |

30 |

O |

Dient

zur Steuerung des externen Adresslatches für das zeitliche Demultiplexen der

Daten und Adressen. Es wird alle 6 Oszillatorperioden bei externem

Speicherzugriff aktiviert. |

|

P0.0-P0.7 |

39-32 |

I/O |

Port

0 ist ein bidirektionaler open drain I/O Port. Wird auch für die Adressen und

Daten verwendet bei der zweiten Betriebsart. |

|

P1.0-P1.7 |

1-8 |

I/O |

Ist

ein 8-Bit quasibidirektionaler Ein-, Ausgangsport. |

|

P2.0-P2.7 |

21-28 |

I/O |

Ist

ein 8-Bit quasibidirektionaler Ein-, Ausgangsport. In der zweiten Betriebsart

stellt er die oberen acht Bit der Adressen zur Verfügung. |

|

P3.0-P3.7 |

10-17 |

I/O |

Ist

ein 8-Bit quasibidirektionaler Ein-, Ausgangsport. In der zweiten Betriebsart

stellt er wichtige alternative Funktionen zur Verfügung. |

|

|

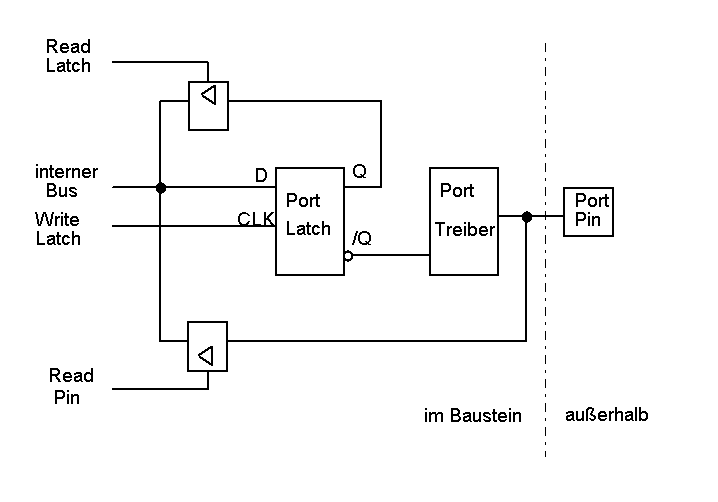

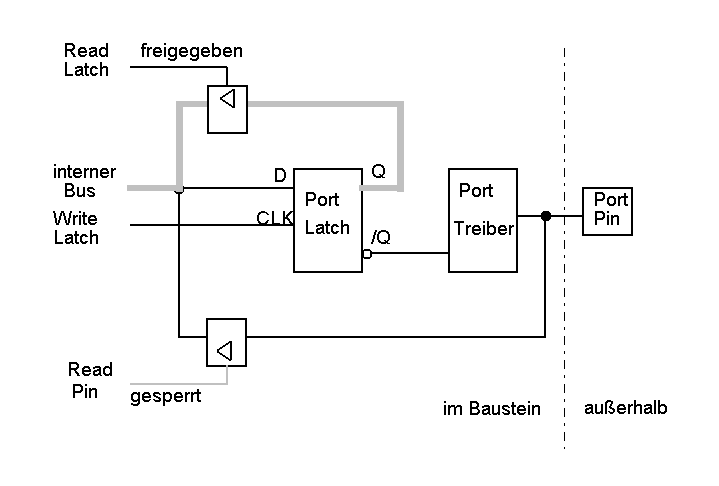

Bild

3.2. Prinzipieller Aufbau eines 8051-Ports

|

|

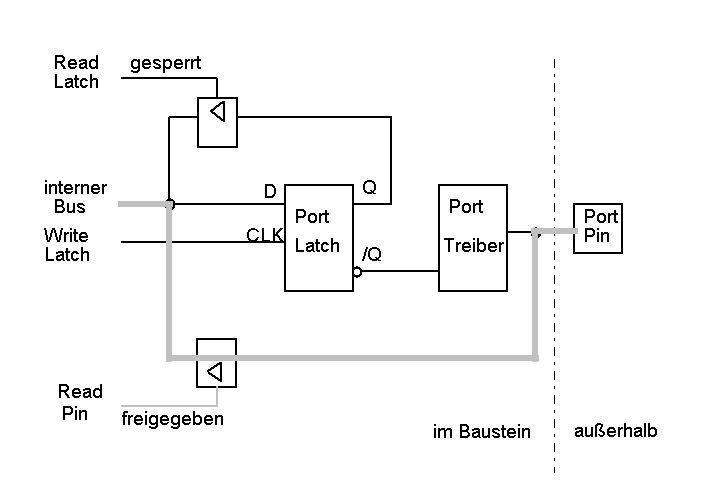

Bild

3.3. Datenweg: Zustand des Port-Pins lesen

|

|

Bild

3.4. Datenweg: Pin beschreiben mit Speichern

Bild

3.5. Zustand des Port-Latches lesen

|

|

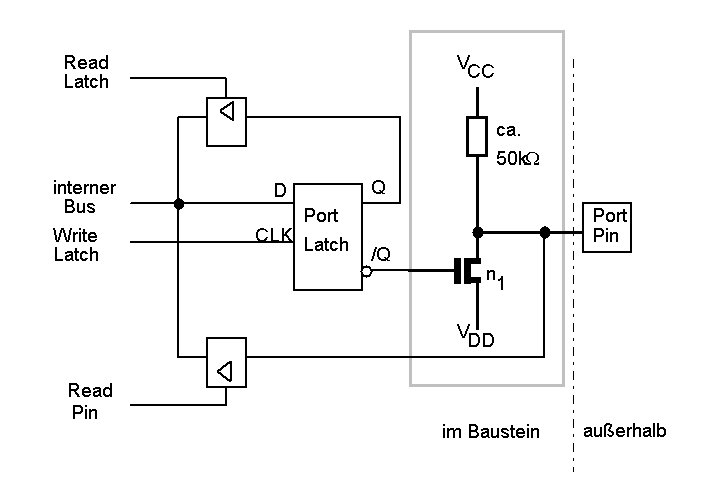

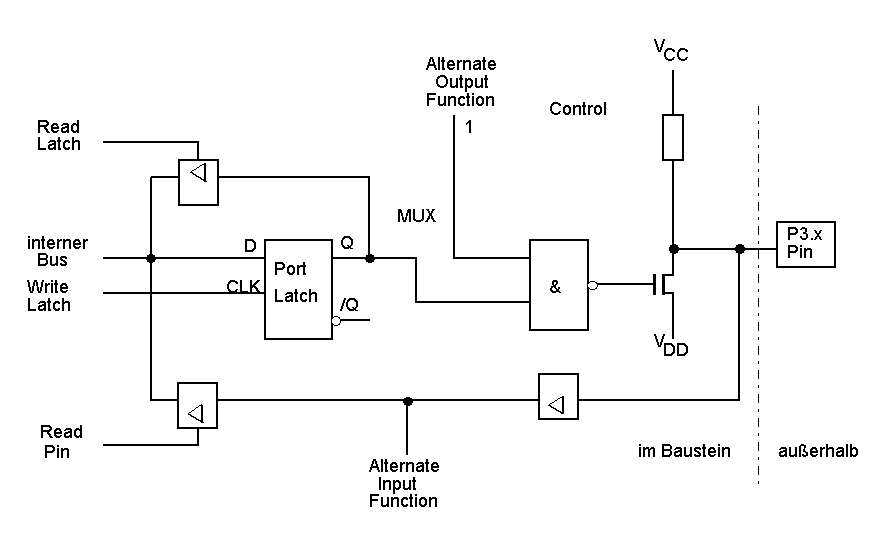

Bild

3.6. Aufbau des Treiberbausteins Port 1 bis 5

|

|

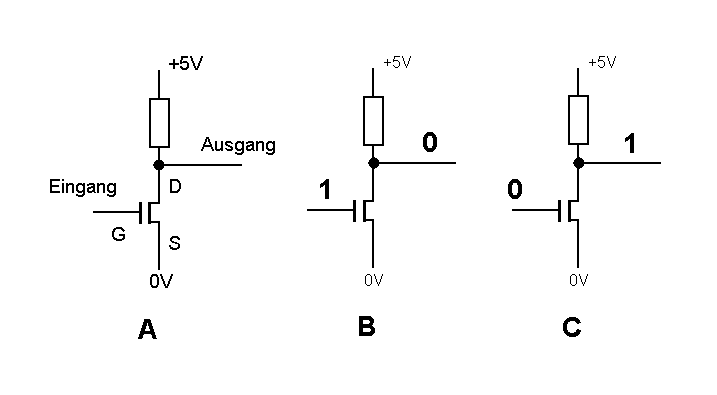

Bild

3.7. Funktionsweise der FET’s im Controller

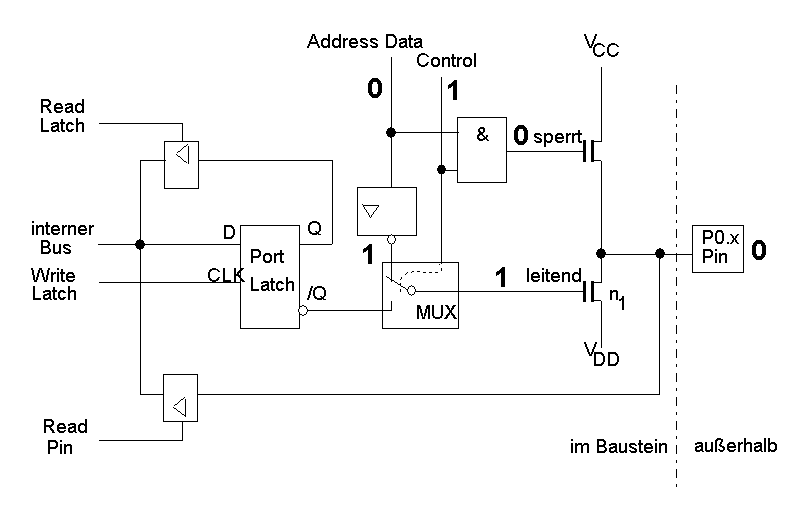

Bild

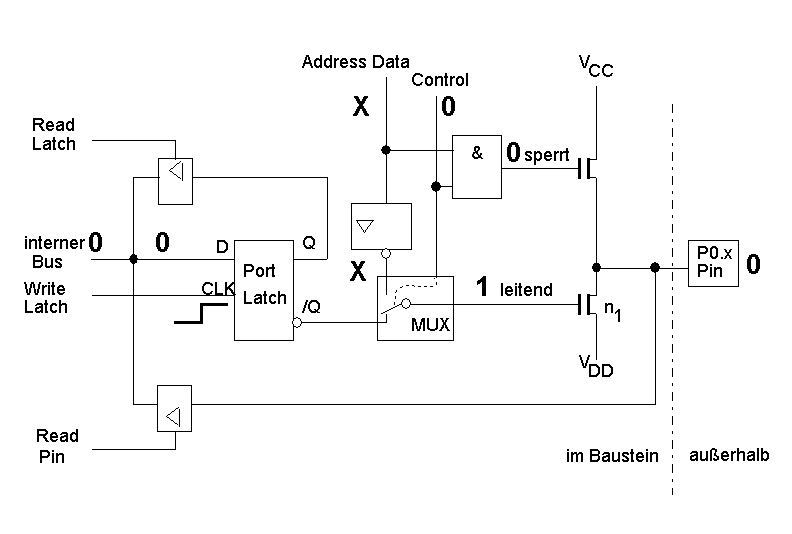

3.8. Port 0 als Adressausgang mit 0-Pegel am Ausgang

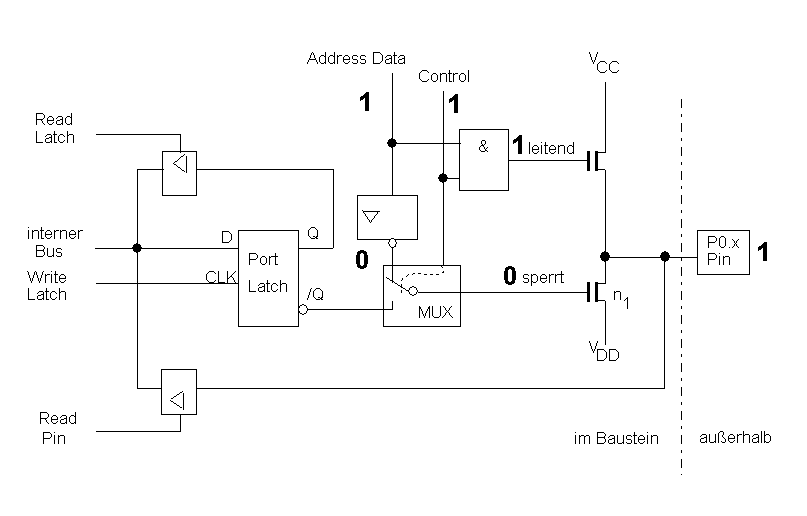

Bild

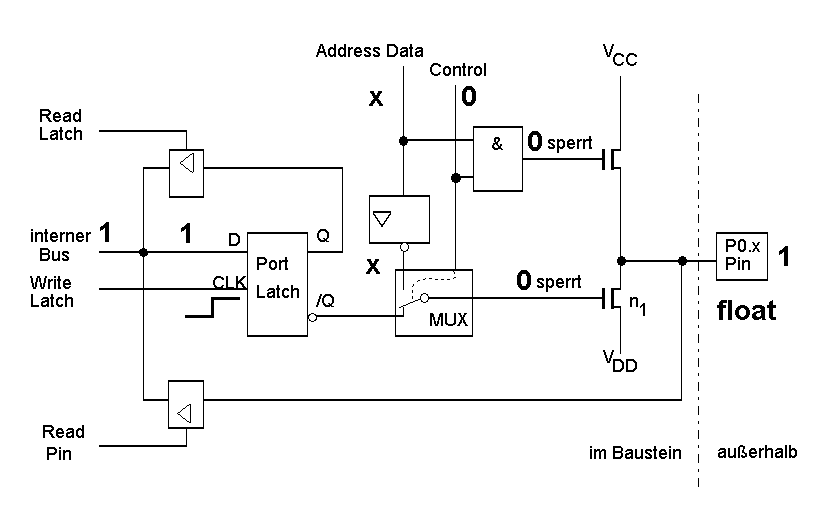

3.9. Port 0 als Adressausgang mit 1-Pegel am Ausgang

Bild

3.10. Port 0 als Datenausgang mit 0-Pegel

Bild

3.11. Port 0 als Datenausgang mit 1-Pegel am Ausgang

Bild

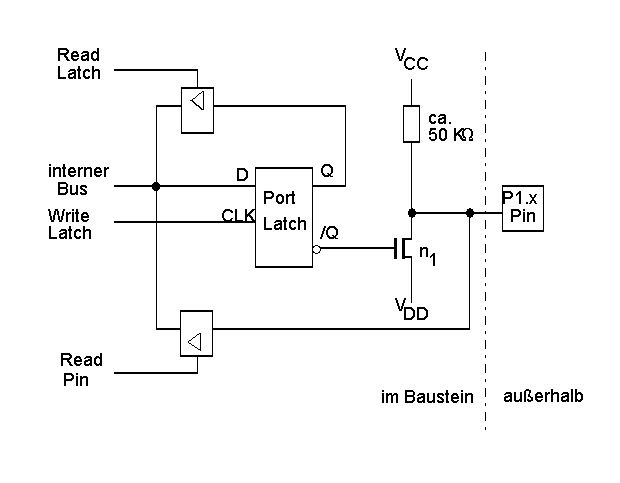

3.12. Port 1 als bidirektionaler Port mit internem

Pull-up Widerstand

Bild

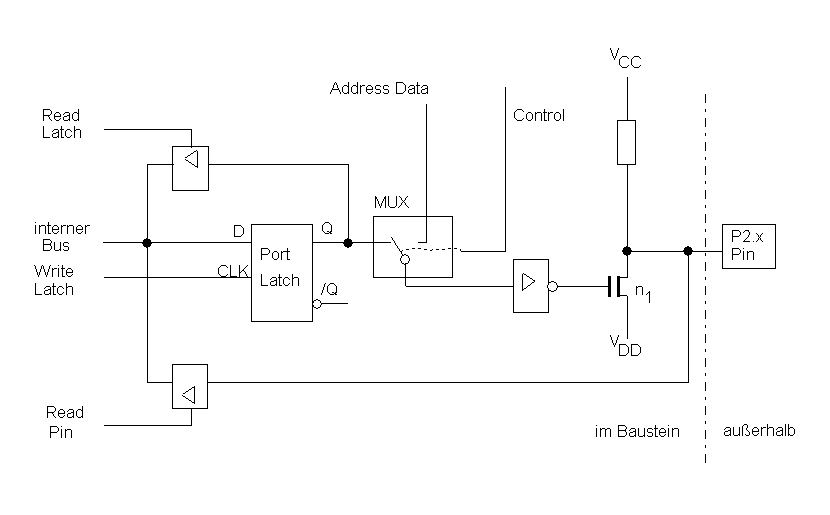

3.13. Port 2 als bidirektionaler Port mit internem

Pull-up-Widerstand

Bild

3.14. Port 3 als bidirektionaler Port mit Alternate

Functions

Tabelle

3.2. Alternative Funktionen an Port 3

|

Port

Pin |

Bezeichnung |

Ein-,

Ausgang |

Alternative

Funktionen |

|

P3.0 |

RxD

|

Eingang |

serieller

Empfang |

|

P3.1 |

TxD |

Ausgang |

serielles

Senden |

|

P3.2 |

/INT0 |

Eingang |

Interrupt

0 |

|

P3.3 |

/INT1 |

Eingang |

Interrupt

1 |

|

P3.4 |

T0 |

Eingang |

Timer 0 |

|

P3.5 |

T1 |

Eingang |

Timer

1 |

|

P3.6 |

/WR |

Ausgang |

externes

Schreibsignal |

|

P3.7 |

/RD |

Ausgang |

externes

Lesesignal |

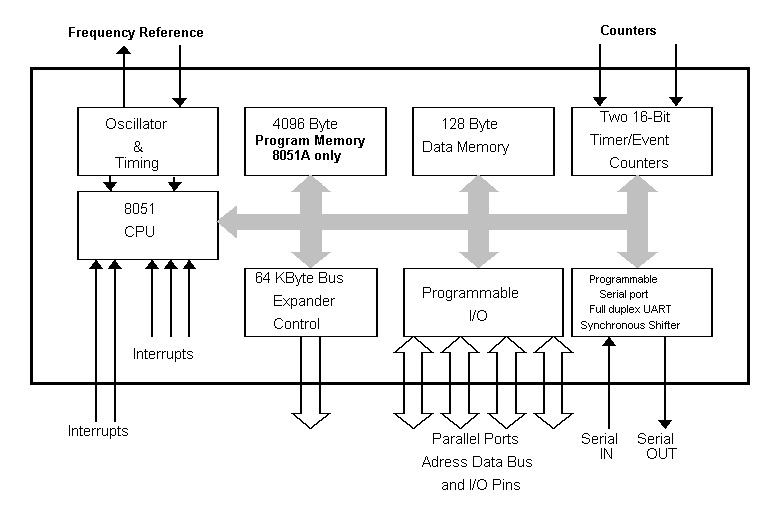

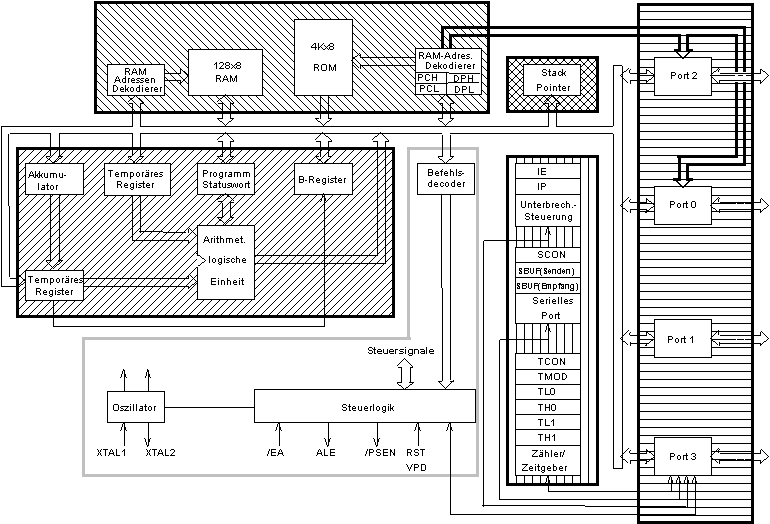

Bild

3.15. Blockdiagramm des 8051 - 8051 A

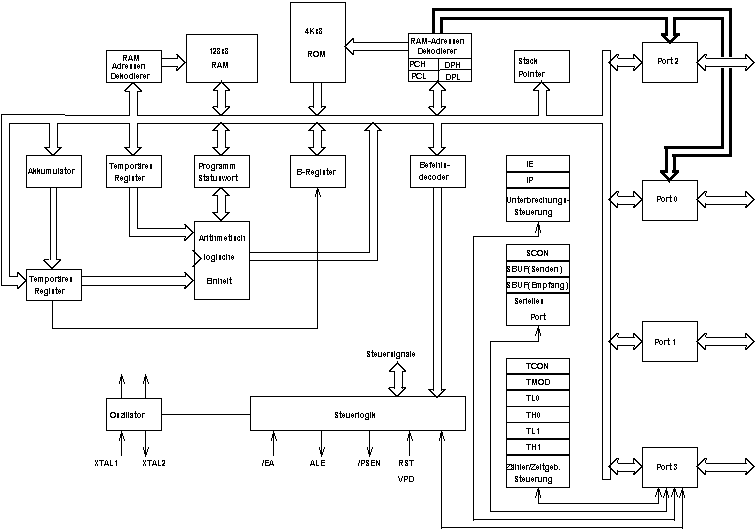

Bild

3.16. Verfeinertes Blockdiagramm des 8051 - 8051 A

Tabelle 3.3.

Verwendete Abkürzungen im verfeinerten Blockbild des 8051

|

Abkürzung |

Bedeutung

engl. |

Erklärung |

|

RAM |

Random Access Memory |

Schreib-

und Lesespeicher |

|

ROM |

Read Only Memory |

Nur-Lesespeicher |

|

PCH |

Program Counter High Byte |

Programmzähler

höherwertiges Byte |

|

PCL |

Program Counter Low Byte |

Programmzähler

niederwertiges Byte |

|

DPH |

Data Pointer High Byte |

Adresszeiger

auf externen Datenspeicher höherwertiges Byte |

|

DPL |

Data Pointer Low Byte |

Adresszeiger

auf externen Datenspeicher niederwertiges Byte |

|

IE |

Interrupt

Enable |

Register

für Unterbrechungsfreigabe |

|

IP |

Interrupt Priority |

Register

für Unterbrechungspriorität |

|

SCON |

Serial Control |

Register

für Einstellungen des seriellen Interface |

|

SBUF |

Serial

Buffer |

Speicher

für Senden |

|

SBUF |

Serial

Buffer |

Speicher

für Empfangen |

|

TCON |

Timer

Control |

Zeitgeber

Kontrolle |

|

TMOD |

Timer Mode |

Register

für Zeitgebereinstellungen - Betriebsart |

|

TL0, TH0 |

Timer 0 Low Byte, Timer 0 High Byte |

Low

Byte, High Byte von Zeitgeber 0 |

|

TL1, TH1 |

Timer 1 Low Byte, Timer 1 High Byte |

Low

Byte, High Byte von Zeitgeber 1 |

|

/EA |

External Address |

Bei

Low-Pegel wird auf die externen Adressen zugegriffen |

|

ALE |

Address Latch Enable |

Signal

für Übernahme der zeitgemultiplexten Adressen |

|

/PSEN |

Program Storage Enable |

Signal

für Zugriff auf externen Programmspeicher |

|

RST / VPD |

Reset / Stand By Power |

Rücksetzen

des Prozessors / Leistungsversorgung |

Tabelle

3.4. Port 3 Alternative Funktionen

|

Pin |

Bedeutung |

|

RxD

|

serieller

Empfang |

|

TxD |

serielles

Senden |

|

/INT0 |

Interrupt 0 |

|

/INT1 |

Interrupt 1 |

|

T0 |

Timer 0 |

|

T1 |

Timer 1 |

|

/WR |

externes

Schreibsignal |

|

/RD |

externes

Lesesignal |

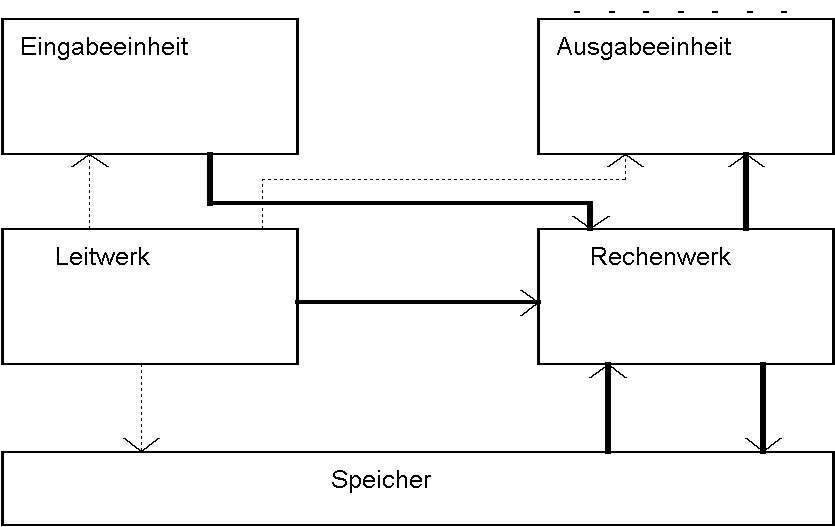

Bild

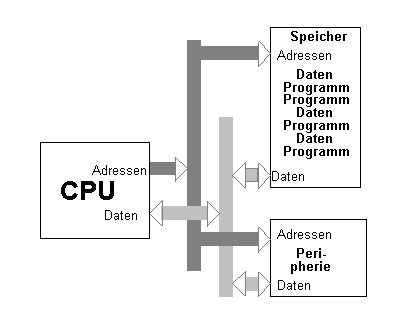

3.17. Klassischer Aufbau eines Digitalrechners

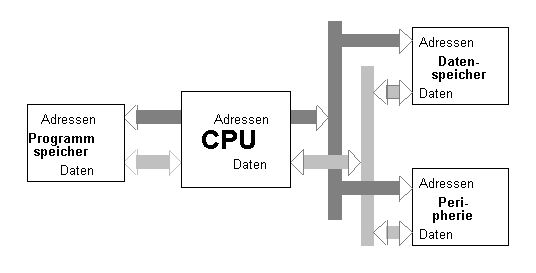

Bild

3.18. Verfeinertes Blockdiagramm des 8051 mit

Zuordnungen zu den Einheiten eines Digitalrechners

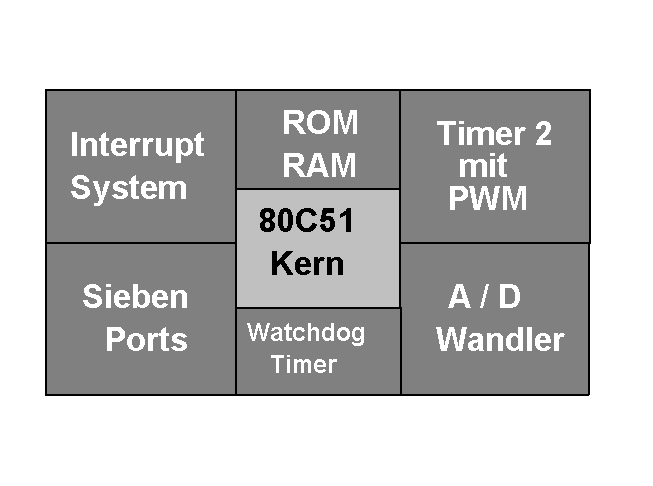

Bild

3.19. 80C535 Erweiterungen

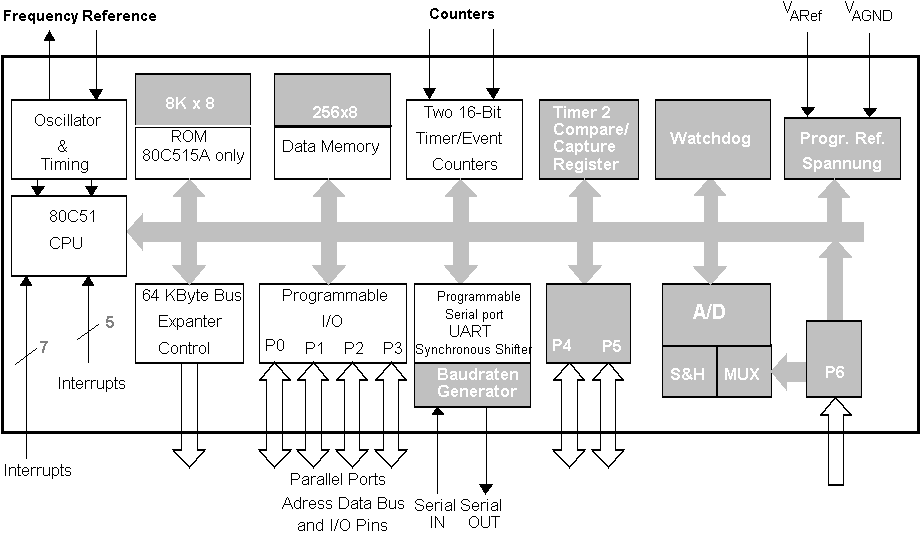

Bild

3.20. 80C515 / 80535 Blockdiagramm (grau - zum 8051

zusätzliche Einheiten)